Advanced packaging is a concept derived from advanced wafer processes, generally refers to packaging technology that integrates different systems into the same package to achieve more efficient system performance. In other words, any packaging technology that can enhance the overall performance of the chip (including transmission speed, computing speed, etc.) can be considered advanced packaging. The corresponding traditional packaging involves individually packaging each chip and then assembling these packaged chips onto a PCB motherboard to form a complete system. The interconnection of electrical signals is achieved through the PCB board. In the industry, the upright packaging of chips is generally classified as traditional packaging, where chips are connected to each other (or to PCB boards) through gold bonding wires. Advanced packaging generally refers to the flip-chip packaging form, where chips are interconnected through solder bumps between chips (or between chips and PCB boards). In general, the longer the distance between chips and the slower the information transfer, the lower the performance of the chipset system. Consequently, at the same chip level, advanced packaging has shorter transmission distances, resulting in stronger system performance.

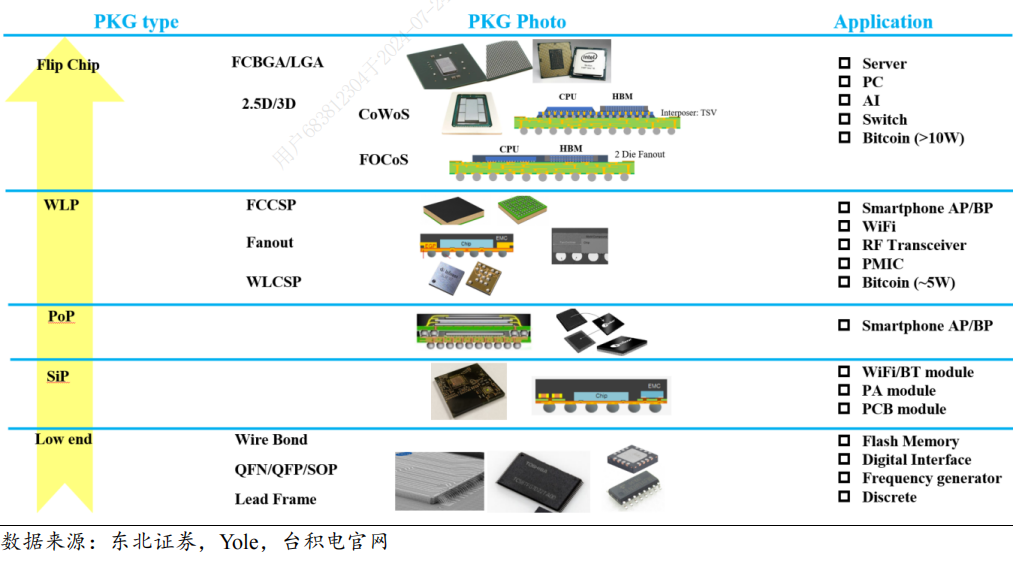

Advanced packaging can be roughly divided into two major categories, namely Flip Chip and Wafer Level Package (WLP). In recent years, based on these two types of packaging forms, a variety of specific packaging processes have been derived, including FCBGA, FCLGA, 2.5D/3D packaging, Fanout, FCCSP and so on. Although many advanced packaging technologies have only slight differences, due to the customized product requirements of customers in different application fields, a large number of different types of advanced packaging have emerged in the industry.

From the perspective of downstream applications, application scenarios that require high transmission rates, such as servers, AI chips, PCs, switches, and high-power mining machines, mostly adopt the Flip Chip packaging process. While smartphones, WiFi, RF chips, power management chips, and low-power mining machines usually adopt the WLP packaging process. For low transmission and low computing power application scenarios such as flash memory and discrete devices, only traditional packaging in the form of wire bonding (Wire Bond), pins (QFN/QFP/SOP) or lead - frame is required.

(Package Type Panorama)

(Package Type Panorama)

(Advanced Package Type Diagram)

(Advanced Package Type Diagram)

The market scale of traditional packaging is larger, but the growth rate of advanced packaging is remarkable. According to Yole data, the global advanced packaging market size was $44.3 billion in 2022 and is expected to grow at a CAGR of 10.03% from 2022-2028, reaching $78.6 billion in 2028. However, the growth rate of traditional packaging is relatively slow. In 2022, the global market size of traditional packaging was 50.7 billion U.S. dollars. The compound growth rate from 2022 to 2028 is only 4.15%. It is expected that the market size of traditional packaging will reach 64.7 billion U.S. dollars in 2028, and the global total packaging market size will reach 143.3 billion U.S. dollars. In terms of market share, the global advanced packaging market share was 46.6% in 2022, which is expected to exceed the traditional packaging by 51% in 2025, and the share will further increase to 54.8% in 2028.

Since semiconductor processes entered 10nm, Moore's Law has become obsolete, meaning that the chip iteration no longer meets‘the number of transistors integrated into an integrated circuit chip doubles every 18 months, and the performance of microprocessors doubles every 18 months while halving its price.’ In the post-Moore's Law era, the advanced packaging is an effective way for the industry.

Die bonder is the most critical and core equipment in the die attach process of semiconductor post packaging and testing.

The bonding machine is mainly used for the mounting of bare chips or micro electronic components. The chip is mounted on the lead frame, heat sink, substrate, or directly mounted on the PCB board to achieve electrical connection between the chip and the outside. In general, chip bonding requires not only that the packaged chip product can withstand the physical pressure of subsequent assembly and dissipate the heat generated during chip operation, but also that it must maintain constant conductivity and achieve high levels of insulation.

Therefore, as chip sizes become smaller and performance requirements continue to increase, bonding technology has become more and more important, and bonding equipment has become a key part of semiconductor packaging equipment, carrying the progress of bonding technology. The bonding process can generally be divided into two types: traditional bonding and advanced bonding. Traditional methods require the simultaneous involvement of die bonder and wire bonder.

The traditional method consists of Die Attach and Wire Bonding. In the die attach process, the adhesive is first applied to the package substrate, and then the chip is placed on the substrate with the top side facing up. Then, the pad points on the front of the chip are connected to the frame or substrate pads through a wire bonder, which is currently a mature process. Due to the two-step bonding process, two types of equipment are required: die bonder and wire bonder.

According to VLSI, global market size of die bonder is expected to reach 1.5 billion US dollars in 2024, with LED as an important downstream application. And (advanced) die bonder is expected to become the packaging equipment with the fastest market growth rate in the next five years. According to China Economic Industry Research Institute, it is expected that the market size of semiconductor die bonder in China will reach 5.1 billion yuan in 2024 and 8.1 billion yuan in 2029, with a GAGR of about 9.7% from 2024 to 2029. The die bonder equipment is dominated by overseas companies, and there is a vast space for domestic substitution.

Packaging technology has gone through an evolution from the initial lead frame to Flip Chip, TCP, Fan-out Package, Hybrid Bonding, and the direction of technology development is more I/O, thinner thickness to carry more complex chip functions and adapt to thinner and lighter mobile devices.

In this process, the density of bonding has been improved from 5-10/mm2 to 10k+/mm2, and the accuracy has been improved from 20-10um to 0.5-0.1um. Meanwhile, the energy/Bit is further reduced to 0.05 pJ/Bit, which puts forward higher requirements for the control accuracy and working efficiency of die bonder.

There are two major application methods of hybrid bonding. W2W is relatively mature, and D2W has a wider prospect. The first hybrid bonding method is wafer to wafer (W2W, Wafer to Wafer), mainly used for CIS and NAND products.

As the core process of heterogeneous integration, W2W hybrid bonding has achieved a good successful record in CMOS image sensors and various memory and logic technologies. Cu-Cu hybrid bonding first appeared in 2016, when SONY used Cu-Cu hybrid bonding between the lower circuit chip and the upper pixel chip of the stacked CMOS image sensor.

For the field of semiconductor die bonder equipment, we can provide high-speed, high-acceleration direct-drive motion platform based on years of experience in developing precision motion systems. Innovative balanced mass damping technology is available for shocks caused by high acceleration.

For Z-axis, the core component solutions such as maglev voice coil motors, active water-cooled voice coil motor and magnetic spring can be customized, which can effectively improve the accuracy of Z-axis and reduce the risk of Z-axis heating. Through the highly modular design, it is easier for customers to achieve great configuration flexibility at a low cost.

Our after-sales team covers all major cities in China to provide you with a full range of technical support.

(The latest industry and technical data comes from websites and other public information sources)